Med den kommande arkitekturen Ice Lake från Intel är det inte bara en ny tillverkningsprocess som står på schemat men även ökade mängder L1D och L2 cache jämfört med tidigare generationer.

Intels övergång till 10 nanometers (nm) tillverkningsteknik från nuvarande 14 nm har varit en lång och krokig väg. Till en början hade processortillverkaren siktet inställt på mitten av år 2015 för en lansering av processorer baserade på den nya tillverkningsprocessen. Dock har Intel stött på flertalet problem med processens utveckling och nu har företaget istället siktet inställt på slutet av år 2019.

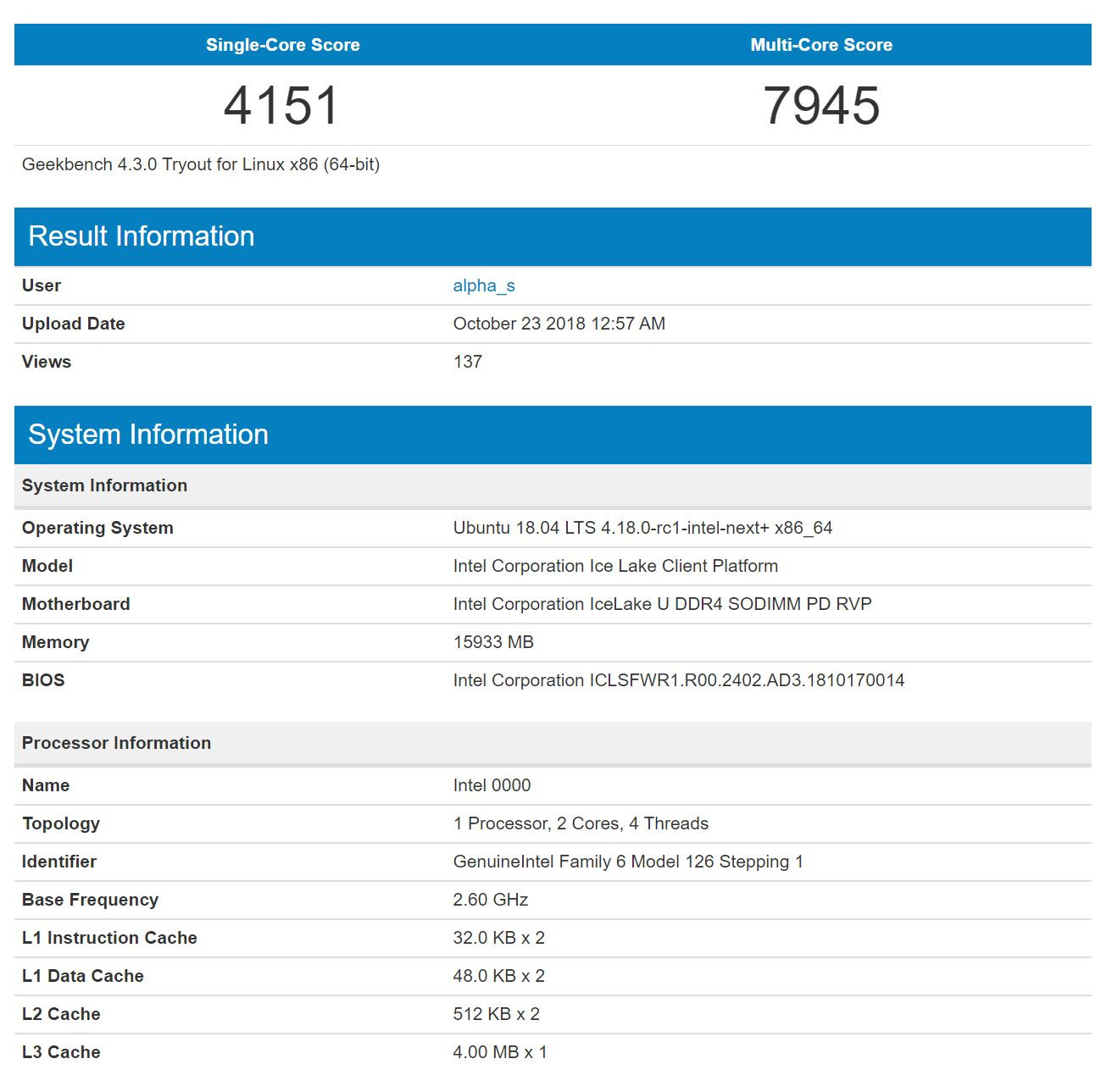

Intels kommande processorarkitektur “Ice Lake” kommer att baseras på den kommande tillverkningsprocessen. Detta är dock inte allt som är nytt med den kommande processorarkitekturen jämfört med sina föregångare. Datorentusiaster med falkögon har upptäckt information angående den kommande arkitekturen i databasen för det syntetiska prestandatestet Geekbench.

I Geekbench databas finns ett inlägg för ett ingenjörsexemplar av en tvåkärnig Intel-processor med fyra trådar baserad på den kommande arkitekturen. Under “L1 Data Cache” och “L2 Cache” kan siffror som inte liknar tidigare arkitekturer skådas.

Mängden L1 Data cache hos Ice Lake listas som 48 kilobyte (KB) per processorkärna. Denna mängd har hos tidigare arkitekturer legat på 32 KB. Mängden L2 cache listas som 512 KB per kärna. Tidigare har det rört sig om 256 KB per kärna.

Huruvida denna tvåkärniga processors cache-mängder är satta i sten och om resterande Ice Lake-baserade “mainstream”-processorer kommer att kunna avnjuta samma behandling återstår att se.