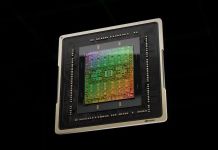

Over at Ars Technica there’s an article that digs deep into the AMDs Hammer processor arcitecture, both Athlon 64 and Opteron. “In my previous work, I’ve looked in some detail at the x86-64 instruction set, but I’ve never talked about the microarchitecture of processors that implement it. The present series of articles fills that gap by taking a close look at the architecture that underlies AMD’s Hammer-based Opteron and Athlon 64 lines. In Part I of this series, we’ll take a look at Hammer’s overall design approach. We’ll also discuss some of the problems with the x86 instruction set that Hammer’s front end is designed to solve, before examining in detail how the processor handles instruction fetching and decoding.” In the article we among others get detailed information on the Hammer’s pipeline design, the integrated memory controller, essentially all important components of the Hammer arcitecture. Loads of interesting reading for those who wants to know more about processors. The article can be found here.

The article is written by Jon “Hannibal” Stokes that has written many similar articles and I have to say he does a very well job dissecting the Hammer arcitecture and making it reasonibly understandable.

Jon also compares with e.g. a PowerPC and how it works.

Subscribe

Please login to comment

0 Comments

äldsta