Det finns inte mycket tillgänglig information angående AMD:s kommande APU-enheter som baseras på arkitekturen Zen 2, produkter som går under kodnamnet Renoir har dock i ett nytt rykte hävdats utrustas med Vega-grafik med upp till 12 beräkningsenheter.

Under förra veckan lanserade AMD sin senaste APU-enhet Athlon 3000G. Här rör det sig om processorarkitekturen Zen+, två processorkärnor och fyra trådar. Den utrustas även med en integrerad grafikkrets baserad på arkitekturen Vega. Mer exakt är det “Vega 3”-grafik vilket innebär att kretsen utrustats med endast tre beräkningsenheter.

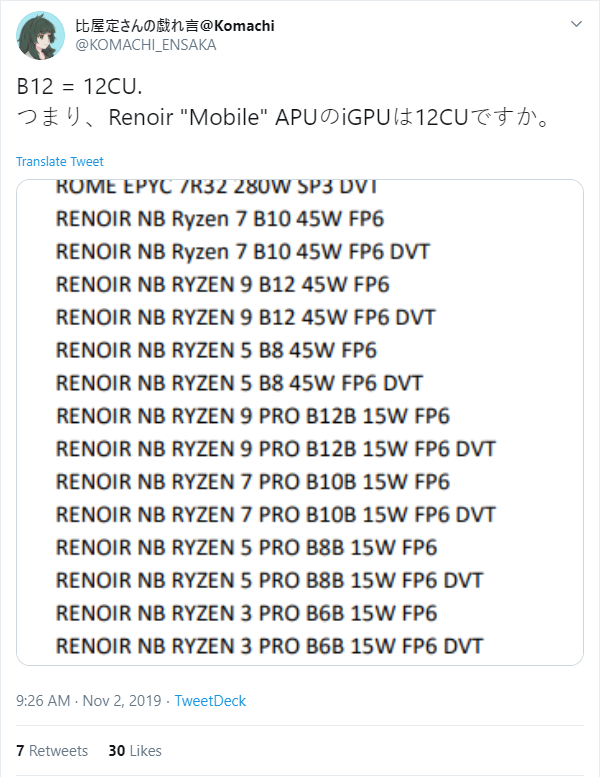

Nästa generations APU-enheter ryktas nu kunna ta ett rejält kliv framåt när det kommer till de integrerade grafikkretsarna. Enligt Twitter-profilen Komachi ska dessa Zen 2-baserade enheter som går under samlingsnamnet Renoir blir tillgängliga i Ryzen 7 och Ryzen 9-varianter. De sistnämnda sägs utrustas med Vega 12-grafik vilket innebär 12 beräkningsenheter.

Det finns ingen information angående antalet processorkärnor dessa enheter skulle kunna utrustas med. Däremot är Zen 2 baserad på 7 nanometers (nm) tillverkningsteknik vilket innebär att fler kärnor kan få plats på processorkretsarna. Genom att inte öka antalet kärnor eller endast lägga till ett fåtal skulle AMD kunna lämna tillräckligt mycket plats för större grafikkretsar.

Twitter-profilen Locuza kommer även med förslag om hur AMD kan välja att konfigurera dessa beräkningsenheters kluster. Här nämns även Vega 13 och Vega 15-grafik. Något Komachi inte nämner i sina egna inlägg.

One good detail to know about GCN5 is that up to 3 CUs share the I$ and K$.

12 is the max unit count with only 4 I$/K$ slices.

13 would mean a new 32KBI$/16KBK$ just for one extra CU.

13 CU confic 1 is very unlikely, confic 2 more realistic but 12 CUs fit nicely or 14/15 CUs. pic.twitter.com/RPhi5AkSYA— Locuza (@Locuza_) November 2, 2019

Värt att påpeka är att det i dagsläget inte finns någon bekräftad information från AMD angående hur många processorkärnor eller beräkningsenheter nästa generations APU-enheter kan komma att utrustas med. Således bör ovanstående information tas med en nypa salt.

Ehh…

Samma källa anger Vega13 för 15W Renoir…

https://twitter.com/KOMACHI_ENSAKA/status/1192864143142838273

https://twitter.com/KOMACHI_ENSAKA/status/1192864065741156352

Sen “Locusa” verkar flumma rätt mycket, vet verkligen inte var han har fått drömt fram att 3 cu delar på cache. Det riktiga är “Four Compute units are wired to share an Instruction Cache 16 KiB in size and a scalar data cache 32KiB in size.” Compute units One compute unit combines 64 shader processors with 4 TMUs.[9][10] The compute unit is separate from, but feed into, the render output units (ROPs).[10] Each Compute Unit consists of a CU Scheduler, a Branch & Message Unit, 4 SIMD Vector Units (each 16-lane wide), 4 64KiB VGPR files, 1 scalar unit, a… Läs hela »